EVALUATION KIT **AVAILABLE**

###

### ±5V, 1.5Gsps, 8-Bit ADC with On-Chip 2.2GHz Track/Hold Amplifier

### **General Description**

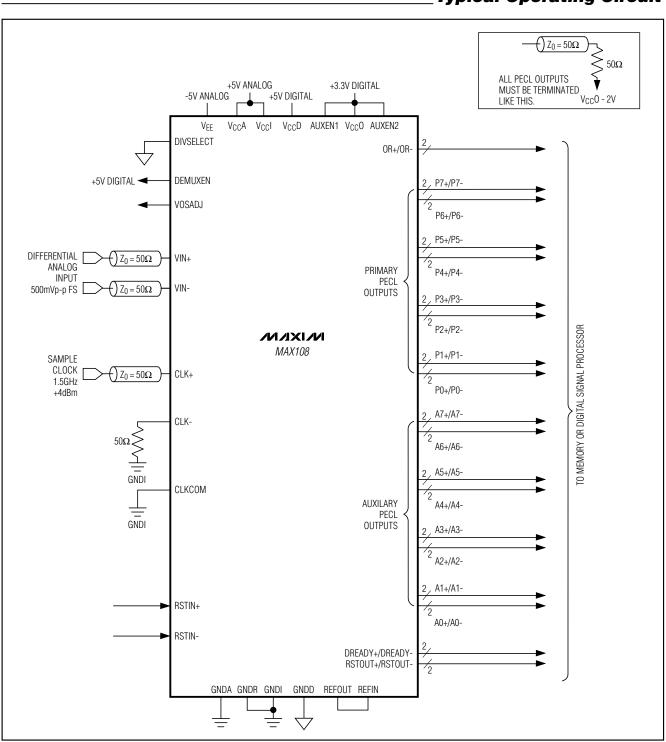

The MAX108 PECL-compatible, 1.5Gsps, 8-bit analogto-digital converter (ADC) allows accurate digitizing of analog signals with bandwidths to 2.2GHz. Fabricated on Maxim's proprietary advanced GST-2 bipolar process, the MAX108 integrates a high-performance track/hold (T/H) amplifier and a quantizer on a single monolithic die.

The innovative design of the internal T/H, which has an exceptionally wide 2.2GHz full-power input bandwidth, results in high performance (typically 7.5 effective bits) at the Nyquist frequency. A fully differential comparator design and decoding circuitry reduce out-of-sequence code errors (thermometer bubbles or sparkle codes) and provide excellent metastable performance. Unlike other ADCs that can have errors resulting in false fullor zero-scale outputs, the MAX108 limits the error magnitude to 1LSB.

The analog input is designed for either differential or single-ended use with a ±250mV input voltage range. Dual, differential, positive-referenced emitter-coupled logic (PECL)-compatible output data paths ensure easy interfacing and include an 8:16 demultiplexer feature that reduces output data rates to one-half the sampling clock rate. The PECL outputs can be operated from any supply between +3V to +5V for compatibility with +3.3V or +5V referenced systems. Control inputs are provided for interleaving additional MAX108 devices to increase the effective system sampling rate.

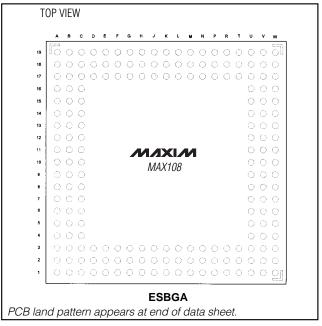

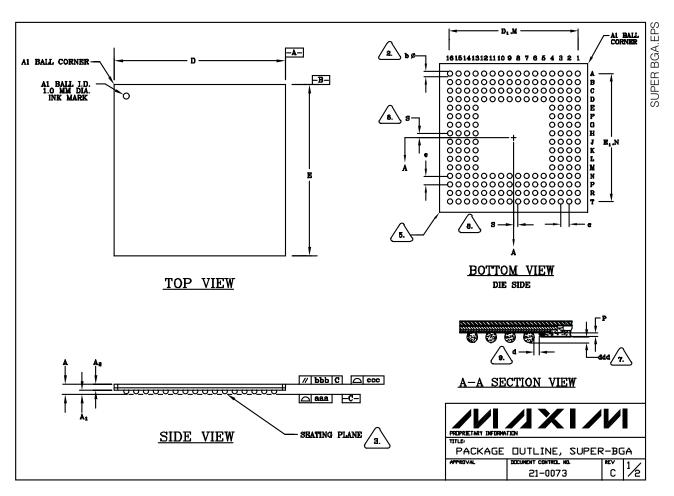

The MAX108 is packaged in a 25mm x 25mm, 192-contact Enhanced Super Ball-Grid Array (ESBGA™) and is specified over the commercial (0°C to +70°C) temperature range. For pin-compatible, lower speed versions of the MAX108, see the MAX104 (1Gsps) and the MAX106 (600Msps) data sheets.

### **Applications**

Digital RF/IF Signal Processing Direct RF Downconversion High-Speed Data Acquisition Digital Oscilloscopes High-Energy Physics Radar/ECM Systems ATE Systems

Typical Operating Circuit appears at end of data sheet.

ESBGA is a trademark of Amkor/Anam.

Features

- ♦ 1.5Gsps Conversion Rate

- ♦ 2.2GHz Full-Power Analog Input Bandwidth

- ♦ 7.5 Effective Bits at f<sub>IN</sub> = 750MHz (Nyquist) Frequency)

- **♦** ±0.25LSB INL and DNL

- **♦ 50**Ω Differential Analog Inputs

- ♦ ±250mV Input Signal Range

- ♦ On-Chip, +2.5V Precision Bandgap Voltage Reference

- ◆ Latched, Differential PECL Digital Outputs

- ♦ Selectable 8:16 Demultiplexer

- ♦ Internal Demux Reset Input with Reset Output

- ♦ 192-Contact ESBGA Package

- ♦ Pin Compatible with MAX104 (1Gsps) and MAX106 (600Msps)

### **Ordering Information**

| PART      | TEMP. RANGE  | PIN-PACKAGE |

|-----------|--------------|-------------|

| MAX108CHC | 0°C to +70°C | 192 ESBGA   |

### 192-Contact ESBGA **Ball Assignment Matrix**

MIXIM

Maxim Integrated Products 1

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> A to GNDAV <sub>CC</sub> D to GNDD |                                    | RSTIN+, RSTIN0.3V to (V <sub>CC</sub> O + 0.3V)<br>VOSADJ Adjust Input0.3V to (V <sub>CC</sub> I + 0.3V) |

|----------------------------------------------------|------------------------------------|----------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub> I to GNDI                          | 0.3V to +6V                        | CLK+ to CLK- Voltage Difference±3V                                                                       |

| V <sub>CC</sub> O to GNDD                          | 0.3V to (V <sub>CC</sub> D + 0.3V) | CLK+, CLK(V <sub>EE</sub> - 0.3V) to (GNDD + 1V)                                                         |

| AUXEN1, AUXEN2 to GND                              | 0.3V to (VccD + 0.3V)              | CLKCOM(VEE - 0.3V) to (GNDD + 1V)                                                                        |

| V <sub>EE</sub> to GNDI                            |                                    | VIN+ to VIN- Voltage Difference±2V                                                                       |

| Between GNDs                                       | 0.3V to +0.3V                      | VIN+, VIN- to GNDI±2V                                                                                    |

| V <sub>CC</sub> A to V <sub>CC</sub> D             | 0.3V to +0.3V                      | Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )                                                    |

| V <sub>CC</sub> A to V <sub>CC</sub> I             | 0.3V to +0.3V                      | 192-Contact ESBGA (derate 61mW/°C above +70°C)4.88W                                                      |

| PECL Digital Output Current                        | 50mA                               | (with heatsink and 200 LFM airflow,                                                                      |

| REFIN to GNDR                                      |                                    | derate 106mW/°C above +70°C)8.48W                                                                        |

| REFOUT Current                                     | +100µA to -5mA                     | Operating Temperature Range                                                                              |

| ICONST, IPTAT to GNDI                              | 0.3V to +1.0V                      | MAX108CHC0°C to +70°C                                                                                    |

| TTL/CMOS Control Inputs                            |                                    | Operating Junction Temperature+150°C                                                                     |

| (DEMUXEN, DIVSELECT)                               | 0.3V to (V <sub>CC</sub> D + 0.3V) | Storage Temperature Range65°C to +150°C                                                                  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC}A = V_{CC}I = V_{CC}D = +5.0V \pm 5\%, V_{EE} = -5.0V \pm 5\%, V_{CC}O = +3.0V \text{ to } V_{CC}D, \text{ REFIN connected to REFOUT, } T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C.)$

| PARAMETER                                   | SYMBOL           | CONDITIONS                                    | MIN   | TYP   | MAX   | UNITS  |

|---------------------------------------------|------------------|-----------------------------------------------|-------|-------|-------|--------|

| ACCURACY                                    |                  |                                               |       |       |       | I.     |

| Resolution                                  | RES              |                                               | 8     |       |       | Bits   |

| Integral Nonlinearity (Note 1)              | INL              | T <sub>A</sub> = +25°C                        | -0.5  | ±0.25 | 0.5   | LSB    |

| Differential Nonlinearity (Note 1)          | DNL              | T <sub>A</sub> = +25°C                        | -0.5  | ±0.25 | 0.5   | LSB    |

| Missing Codes                               |                  | No missing codes guaranteed                   |       |       | None  | Codes  |

| ANALOG INPUTS                               | '                |                                               |       |       |       |        |

| Full-Scale Input Range                      | V <sub>FSR</sub> | Note 1                                        | 475   | 500   | 525   | mVp-p  |

| Common-Mode Input Range                     | V <sub>CM</sub>  | Signal + offset w.r.t. GNDI                   |       | ±0.8  |       | V      |

| Input Resistance                            | RIN              | VIN+ and VIN- to GNDI, T <sub>A</sub> = +25°C | 49    | 50    | 51    | Ω      |

| Input Resistance Temperature<br>Coefficient | TCR              |                                               |       | 150   |       | ppm/°C |

| VOS ADJUST CONTROL INPUT                    |                  |                                               | 1     |       |       | I      |

| Input Resistance (Note 2)                   | Rvos             |                                               | 14    | 25    |       | kΩ     |

| Input Vos Adjust Range                      |                  | VOSADJ = 0 to 2.5V                            | ±4    | ±5.5  |       | LSB    |

| REFERENCE INPUT AND OUTP                    | UT               |                                               |       |       |       |        |

| Reference Output Voltage                    | REFOUT           | Driving REFIN input only                      | 2.475 | 2.50  | 2.525 | V      |

| Reference Output Load<br>Regulation         | ΔREFOUT          | 0 < Isource < 2.5mA                           |       |       | 5     | mV     |

| Reference Input Resistance                  | RREF             | Referenced to GNDR                            | 4     | 5     |       | kΩ     |

### **DC ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC}A = V_{CC}I = V_{CC}D = +5.0V \pm 5\%, \ V_{EE} = -5.0V \pm 5\%, \ V_{CC}O = +3.0V \ to \ V_{CC}D, \ REFIN \ connected \ to \ REFOUT, \ T_A = T_{MIN} \ to \ T_{MAX}, \ unless \ otherwise \ noted. \ Typical \ values \ are \ at \ T_A = +25^{\circ}C.)$

| PARAMETER                                         | SYMBOL           | CONDITIONS                          | MIN    | TYP  | MAX    | UNITS  |

|---------------------------------------------------|------------------|-------------------------------------|--------|------|--------|--------|

| CLOCK INPUTS (Note 3)                             | •                |                                     |        |      |        |        |

| Clock Input Resistance                            | RCLK             | CLK+ and CLK- to CLKCOM, TA = +25°C | 48     | 50   | 52     | Ω      |

| Input Resistance Temperature Coefficient          | TCR              |                                     |        | 150  |        | ppm/°C |

| TTL/CMOS CONTROL INPUTS                           | DEMUXEN,         | DIVSELECT)                          |        |      |        |        |

| High-Level Input Voltage                          | VIH              |                                     | 2.0    |      |        | V      |

| Low-Level Input Voltage                           | V <sub>IL</sub>  |                                     |        |      | 0.8    | V      |

| High-Level Input Current                          | lıH              | V <sub>IH</sub> = 2.4V              |        |      | 50     | μΑ     |

| Low-Level Input Current                           | Ι <sub>Ι</sub> L | V <sub>I</sub> L = 0                | -1     |      | 1      | μΑ     |

| <b>DEMUX RESET INPUT</b> (Note 4)                 |                  |                                     |        |      |        |        |

| Digital Input High Voltage                        | VIH              |                                     | -1.165 |      |        | V      |

| Digital Input Low Voltage                         | VIL              |                                     |        |      | -1.475 | V      |

| PECL DIGITAL OUTPUTS (Note                        | 5)               |                                     |        |      |        |        |

| Digital Output High Voltage                       | Voн              |                                     | -1.025 |      | -0.880 | V      |

| Digital Output Low Voltage                        | Vol              |                                     | -1.810 |      | -1.620 | V      |

| POWER REQUIREMENTS                                |                  |                                     |        |      |        |        |

| Positive Analog Supply Current                    | IccA             |                                     |        | 480  | 780    | mA     |

| Positive Input Supply Current                     | Iccl             |                                     |        | 108  | 150    | mA     |

| Negative Input Supply Current                     | IEE              |                                     | -290   | -210 |        | mA     |

| Digital Supply Current                            | IccD             |                                     |        | 205  | 340    | mA     |

| Output Supply Current (Note 6)                    | IccO             |                                     |        | 75   | 115    | mA     |

| Power Dissipation (Note 6)                        | PDISS            |                                     |        | 5.25 |        | W      |

| Common-Mode Rejection Ratio (Note 7)              | CMRR             | VIN+ = VIN- = ±0.1V                 | 40     | 68   |        | dB     |

| Positive Power-Supply Rejection<br>Ratio (Note 8) | PSRR+            | (Note 9)                            | 40     | 73   |        | dB     |

| Negative Power-Supply<br>Rejection Ratio (Note 8) | PSRR-            | (Note 10)                           | 40     | 68   |        | dB     |

### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC}A = V_{CC}I = V_{CC}D = +5.0V, V_{EE} = -5.0V, V_{CC}O = +3.3V, REFIN connected to REFOUT, fs = 1.5Gsps, f_{IN} at -1dBFS, TA = +25°C, unless otherwise noted.)$

| PARAMETER                            | SYMBOL                | CONDITIONS                                                          |              | MIN   | TYP   | MAX  | UNITS     |

|--------------------------------------|-----------------------|---------------------------------------------------------------------|--------------|-------|-------|------|-----------|

| ANALOG INPUT                         |                       |                                                                     |              | I     |       |      |           |

| Analog Input Full-Power<br>Bandwidth | BW-3dB                |                                                                     |              |       | 2.2   |      | GHz       |

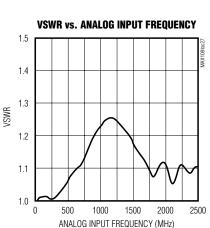

| Analog Input VSWR                    | VSWR                  | fin = 500MHz                                                        |              |       | 1.1:1 |      | V/V       |

| Transfer Curve Offset                | Vos                   | VOSADJ control in                                                   | put open     | -2.0  | 0     | +2.0 | LSB       |

| DYNAMIC SPECIFICATIONS               |                       |                                                                     |              | l .   |       |      |           |

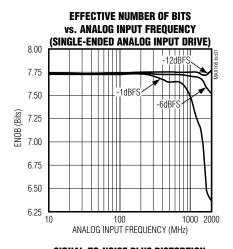

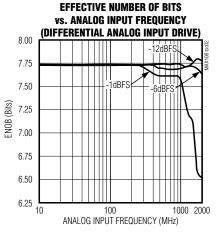

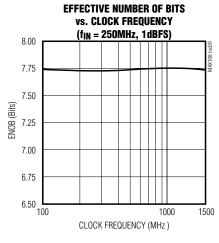

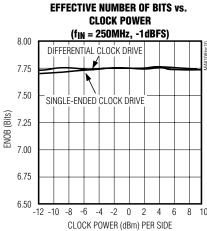

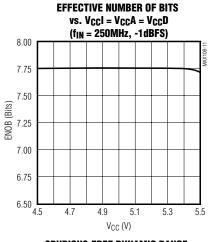

|                                      | ENIOD                 | ( 4500M)                                                            | Differential |       | 7.07  |      |           |

|                                      | ENOB <sub>1500</sub>  | $f_{IN} = 1500MHz$                                                  | Single-ended |       | 7.07  |      |           |

| Effective Number of Bits             | ENIOD                 | ( 7501411                                                           | Differential | 7.1   | 7.51  |      | Б.,       |

| (Note 11)                            | ENOB <sub>750</sub>   | $f_{IN} = 750MHz$                                                   | Single-ended |       | 7.53  |      | Bits      |

|                                      | ENOD                  | f 050M1-                                                            | Differential | 7.3   | 7.71  |      |           |

|                                      | ENOB <sub>250</sub>   | f <sub>IN</sub> = 250MHz                                            | Single-ended |       | 7.71  |      |           |

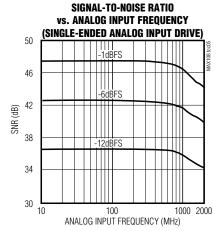

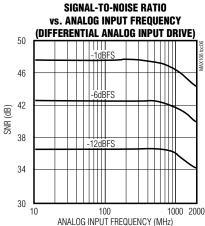

|                                      | CNID                  | f 4500M11-                                                          | Differential |       | 44.8  |      |           |

|                                      | SNR <sub>1500</sub>   | $SNR_{1500}   f_{IN} = 1500MHz$                                     | Single-ended |       | 44.9  |      |           |

| Signal-to-Noise Ratio                | CNID                  | f 750M1-                                                            | Differential | 43.3  | 46.8  |      | - dB      |

| (No Harmonics)                       | SNR <sub>750</sub>    | $f_{IN} = 750MHz$                                                   | Single-ended |       | 46.9  |      |           |

|                                      | ONID                  | ( 0501411                                                           | Differential | 44.2  | 47.4  |      |           |

|                                      | SNR <sub>250</sub>    | f <sub>IN</sub> = 250MHz                                            | Single-ended |       | 47.4  |      |           |

|                                      | TUD                   |                                                                     | Differential |       | -44.5 |      |           |

|                                      | THD <sub>1500</sub>   | $f_{IN} = 1500MHz$                                                  | Single-ended |       | -44.2 |      |           |

| Total Harmonic Distortion            | T. 10                 | ( 750ML                                                             | Differential | -49.0 | -52.1 |      |           |

| (Note 12)                            | THD <sub>750</sub>    | $f_{IN} = 750MHz$                                                   | Single-ended |       | -52.8 |      | dB        |

|                                      | TUD                   | 6 0501411                                                           | Differential | -55.5 | -60.2 |      |           |

|                                      | THD <sub>250</sub>    | f <sub>IN</sub> = 250MHz                                            | Single-ended |       | -61.3 |      | -         |

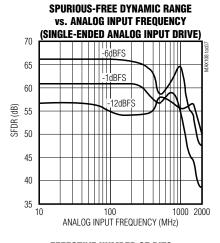

|                                      | OFDD                  | ( 4500M)                                                            | Differential |       | 44.6  |      |           |

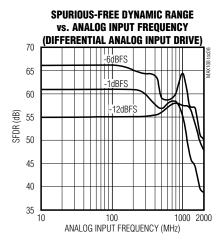

|                                      | SFDR <sub>1500</sub>  | $f_{IN} = 1500MHz$                                                  | Single-ended |       | 45.5  |      |           |

| 0                                    | OFDD                  | ( 750ML                                                             | Differential | 50.0  | 54.0  |      |           |

| Spurious-Free Dynamic Range          | SFDR <sub>750</sub>   | $f_{IN} = 750MHz$                                                   | Single-ended |       | 54.1  |      | dB        |

|                                      | CEDD                  | f 050M1-                                                            | Differential | 55.0  | 61.6  |      |           |

|                                      | SFDR <sub>250</sub>   | $f_{IN} = 250MHz$                                                   | Single-ended |       | 61.7  |      |           |

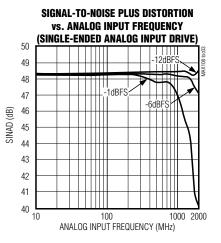

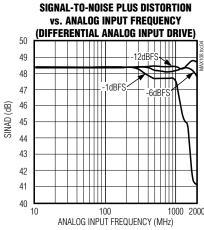

|                                      | OINIAD                | ( 45001411                                                          | Differential |       | 44.3  |      |           |

|                                      | SINAD <sub>1500</sub> | $f_{IN} = 1500MHz$                                                  | Single-ended |       | 44.4  |      |           |

| Signal-to-Noise Ratio and            | CINIAD                | f 7501411                                                           | Differential | 44.5  | 47.0  |      | - dB<br>- |

| Distortion (Note 11)                 | SINAD <sub>750</sub>  | f <sub>IN</sub> = 750MHz                                            | Single-ended |       | 47.1  |      |           |

|                                      | CINIAD                | f 050M1-                                                            | Differential | 45.7  | 48.2  |      |           |

|                                      | SINAD <sub>250</sub>  | $f_{IN} = 250MHz$                                                   | Single-ended |       | 48.2  |      |           |

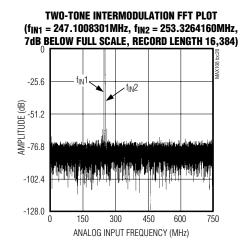

| Two-Tone Intermodulation             | IMD                   | f <sub>IN1</sub> = 247MHz, f <sub>IN2</sub><br>at -7dB below full-s |              |       | -66.8 |      | dB        |

#### AC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CCA} = V_{CCI} = V_{CCD} = +5.0V, V_{EE} = -5.0V, V_{CCO} = +3.3V, REFIN connected to REFOUT, f_S = 1.5Gsps, f_{IN} at -1dBFS, T_A = +25°C unless otherwise noted.)$

| PARAMETER                                     | SYMBOL   | COND                             | CONDITIONS                       |     | TYP  | MAX | UNITS  |

|-----------------------------------------------|----------|----------------------------------|----------------------------------|-----|------|-----|--------|

| TIMING CHARACTERISTICS                        | 1        |                                  |                                  |     |      |     |        |

| Maximum Sample Rate                           | fMAX     |                                  |                                  | 1.5 |      |     | Gsps   |

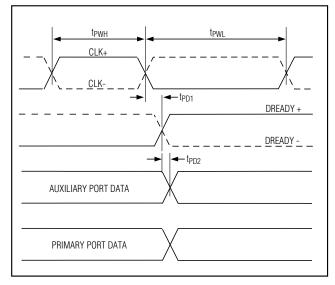

| Clock Pulse Width Low                         | tpwL     | Figure 17                        |                                  | 0.3 |      |     | ns     |

| Clock Pulse Width High                        | tpwH     | Figure 17                        |                                  | 0.3 |      | 5   | ns     |

| Aperture Delay                                | tad      | Figure 4                         |                                  |     | 100  |     | ps     |

| Aperture Jitter                               | taj      | Figure 4                         |                                  |     | <0.5 |     | ps     |

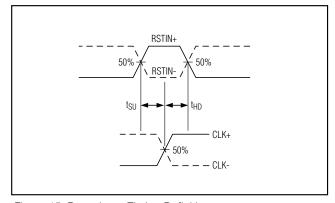

| Reset Input Data Setup Time (Note 13)         | tsu      | Figure 15                        |                                  | 0   |      |     | ps     |

| Reset Input Data Hold Time (Note 13)          | tHD      | Figure 15                        | Figure 15                        |     |      |     | ps     |

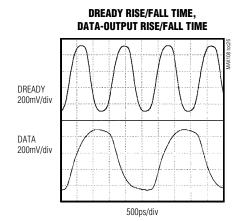

| CLK to DREADY Propagation<br>Delay            | tPD1     | Figure 17                        | Figure 17                        |     | 2.2  |     | ns     |

| DREADY to DATA Propagation<br>Delay (Note 14) | tPD2     | Figure 17                        | Figure 17                        |     | 150  | 350 | ps     |

| DATA Rise Time                                | trdata   | 20% to 80%, CL = 3pF             | Ī                                |     | 420  |     | ps     |

| DATA Fall Time                                | tFDATA   | 20% to 80%, C <sub>L</sub> = 3pF | Ξ                                |     | 360  |     | ps     |

| DREADY Rise Time                              | trdready | 20% to 80%, CL = 3pF             | 20% to 80%, C <sub>L</sub> = 3pF |     | 220  |     | ps     |

| DREADY Fall Time                              | tFDREADY | 20% to 80%, C <sub>L</sub> = 3pF |                                  |     | 180  |     | ps     |

| Primary Port Pipeline                         | topp     | DIV1, DIV2 modes                 |                                  |     | 7.5  |     | Clock  |

| Delay                                         | tPDP     | Figures 6, 7, 8                  | DIV4 mode                        |     | 7.5  |     | Cycles |

| Auxiliary Port Pipeline                       | tpda     | Figures 6, 7, 8                  | DIV1, DIV2 modes                 |     | 8.5  |     | Clock  |

| Delay                                         | 'FDA     | 1 194100 0, 7, 0                 | DIV4 mode                        |     | 9.5  |     | Cycles |

- **Note 1:** Static linearity parameters are computed from a "best-fit" straight line through the code transition points. The full-scale range (FSR) is defined as 256 times the slope of the line.

- **Note 2:** The offset control input is a self-biased voltage divider from the internal +2.5V reference voltage. The nominal open-circuit voltage is +1.25V. It may be driven from an external potentiometer connected between REFOUT and GNDI.

- **Note 3:** The clock input's termination voltage can be operated between -2.0V and GNDI. Observe the absolute maximum ratings on the CLK+ and CLK- inputs.

- Note 4: Input logic levels are measured with respect to the V<sub>CC</sub>O power-supply voltage.

- Note 5: All PECL digital outputs are loaded with 50Ω to V<sub>CC</sub>O 2.0V. Measurements are made with respect to the V<sub>CC</sub>O power-supply voltage.

- **Note 6:** The current in the V<sub>CC</sub>O power supply does not include the current in the digital output's emitter followers, which is a function of the load resistance and the V<sub>TT</sub> termination voltage.

- **Note 7:** Common-mode rejection ratio (CMRR) is defined as the ratio of the change in the transfer-curve offset voltage to the change in the common-mode voltage, expressed in dB.

- **Note 8:** Power-supply rejection ratio (PSRR) is defined as the ratio of the change in the transfer-curve offset voltage to the change in power-supply voltage, expressed in dB.

- Note 9: Measured with the positive supplies tied to the same potential; VCCA = VCCD = VCCI. VCC varies from +4.75V to +5.25V.

- **Note 10:** VEE varies from -5.25V to -4.75V.

- Note 11: Effective number of bits (ENOB) and signal-to-noise plus distortion (SINAD) are computed from a curve fit referenced to the theoretical full-scale range.

- Note 12: Total harmonic distortion (THD) is computed from the first five harmonics.

- Note 13: Guaranteed by design with a reset pulse width one clock period long or greater.

- Note 14: Guaranteed by design. The DREADY to DATA propagation delay is measured from the 50% point on the rising edge of the DREADY signal (when the output data changes) to the 50% point on a data output bit. This places the falling edge of the DREADY signal in the middle of the data output valid window, within the differences between the DREADY and DATA rise and fall times, which gives maximum setup and hold time for latching external data latches.

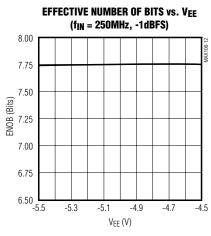

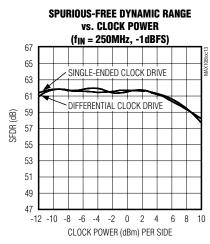

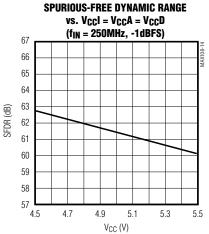

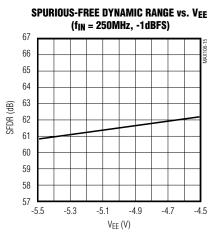

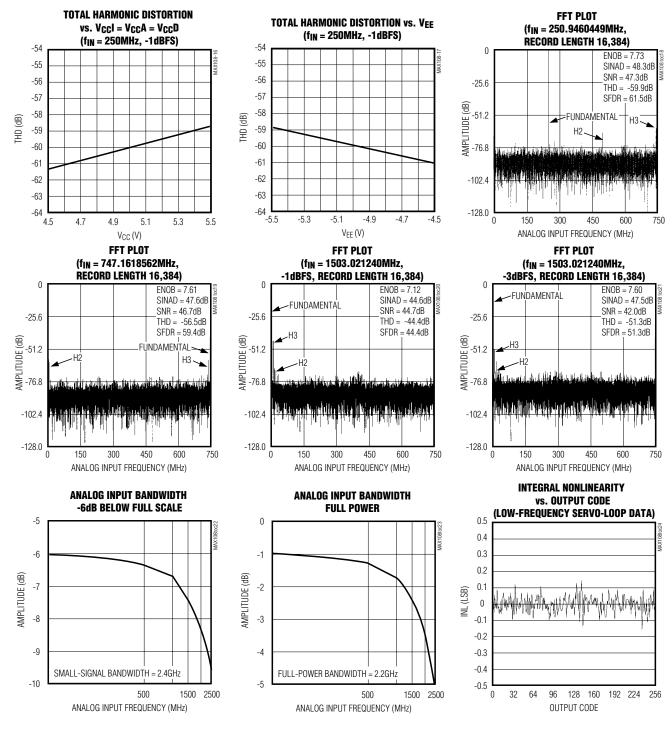

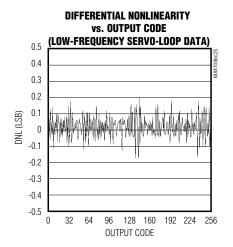

### **Typical Operating Characteristics**

$(V_{CC}A = V_{CC}I = V_{CC}D = +5V, V_{EE} = -5V, V_{CC}O = +3.3V, REFIN connected to REFOUT, f_S = 1.5Gsps, T_A = +25°C, unless otherwise noted.)$

### **Typical Operating Characteristics (continued)**

$(V_{CC}A = V_{CC}I = V_{CC}D = +5V, V_{EE} = -5V, V_{CC}O = +3.3V, REFIN connected to REFOUT, fs = 1.5Gsps, TA = +25°C, unless otherwise noted.)$

### Typical Operating Characteristics (continued)

$(V_{CC}A = V_{CC}I = V_{CC}D = +5V, V_{EE} = -5V, V_{CC}O = +3.3V, REFIN connected to REFOUT, fs = 1.5Gsps, T_A = +25°C, unless otherwise noted.)$

### **Typical Operating Characteristics (continued)**

$(V_{CC}A = V_{CC}I = V_{CC}D = +5V, V_{EE} = -5V, V_{CC}O = +3.3V, REFIN connected to REFOUT, fs = 1.5Gsps, TA = +25°C, unless otherwise noted.)$

### Pin Description

| CONTACT                                                                                                | NAME              | FUNCTION                                                                                                            |

|--------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------|

| A1–A4, A6, A7, B1, B2, C1, C2, D1–D3, G1, H1, J2, J3, K1–K3, L2, L3, M1, N1, T2, T3, U1, V1, V2, W1–W4 | GNDI              | Analog Ground. For T/H amplifier, clock distribution, bandgap reference, and reference amplifier.                   |

| A5, B5, C5, H2, H3, M2, M3, U5, V5, W5                                                                 | Vccl              | Analog Supply Voltage, +5V. Supplies T/H amplifier, clock distribution, bandgap reference, and reference amplifier. |

| A8, B8, C8, U6, V6, W6                                                                                 | GNDA              | Analog Ground. For comparator array.                                                                                |

| A9, B9, C9, U7, V7, W7                                                                                 | V <sub>CC</sub> A | Analog Supply Voltage, +5V. Supplies analog comparator array.                                                       |

| A10, E17, F2, P3, R17, R18                                                                             | TESTPOINT (T.P.)  | Test Point. <b>Do not connect.</b>                                                                                  |

| A11, B11, B16, B17, C11, C16, U9, U17, V9, V17, V18, W9                                                | GNDD              | Digital Ground                                                                                                      |

### Pin Description (continued)

| CONTACT                                                                                          | NAME              | FUNCTION                                                                                                            |  |

|--------------------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------|--|

| A12–A19, B19, C19, D19, E19, F19, G19, H19, J19, K19, L19, M19, N19, P19, T19, U19, V19, W10–W19 | V <sub>CC</sub> O | PECL Supply Voltage, +3V to +5V                                                                                     |  |

| B3, B4, C3, C4, E3, F3, G2, G3, N2, N3, U2–U4, V3, V4                                            | V <sub>EE</sub>   | Analog Supply Voltage, -5V. Supplies T/H amplifier, clock distribution, bandgap reference, and reference amplifier. |  |

| B6, B7                                                                                           | GNDR              | Reference Ground. Must be connected to GNDI.                                                                        |  |

| B10, B18, C10, C17, C18, T17, T18, U8, U18, V8, W8                                               | VccD              | Digital Supply Voltage, +5V                                                                                         |  |

| B12                                                                                              | P0+               | Primary Output Data Bit 0 (LSB)                                                                                     |  |

| B13                                                                                              | A0+               | Auxiliary Output Data Bit 0 (LSB)                                                                                   |  |

| B14                                                                                              | P1+               | Primary Output Data Bit 1                                                                                           |  |

| B15                                                                                              | A1+               | Auxiliary Output Data Bit 1                                                                                         |  |

| C6                                                                                               | REFIN             | Reference Input                                                                                                     |  |

| C7                                                                                               | REFOUT            | Reference Output                                                                                                    |  |

| C12                                                                                              | P0-               | Complementary Primary Output Data Bit 0 (LSB)                                                                       |  |

| C13                                                                                              | A0-               | Complementary Auxiliary Output Data Bit 0 (LSB)                                                                     |  |

| C14                                                                                              | P1-               | Complementary Primary Output Data Bit 1                                                                             |  |

| C15                                                                                              | A1-               | Complementary Auxiliary Output Data Bit 1                                                                           |  |

| D17                                                                                              | DIVSELECT         | TTL/CMOS Demux Divide Selection Input 1: Decimation DIV4 mode 0: Demultiplexed DIV2 mode                            |  |

| D18                                                                                              | AUXEN2            | Connect to V <sub>CC</sub> O to power the auxiliary port, or connect to GNDD to power down.                         |  |

| E1                                                                                               | ICONST            | Die Temperature Measurement Test Point. See <i>Die Temperature Measurement</i> section.                             |  |

| E2                                                                                               | IPTAT             | Die Temperature Measurement Test Point. See <i>Die Temperature Measurement</i> section.                             |  |

| E18                                                                                              | DEMUXEN           | TTL/CMOS Demux Enable Control 1: Enable Demux 0: Disable Demux                                                      |  |

| F1                                                                                               | VOSADJ            | Offset Adjust Input                                                                                                 |  |

| F17                                                                                              | P2-               | Complementary Primary Output Data Bit 2                                                                             |  |

| F18                                                                                              | P2+               | Primary Output Data Bit 2                                                                                           |  |

| G17                                                                                              | A2-               | Complementary Auxiliary Output Data Bit 2                                                                           |  |

| G18                                                                                              | A2+               | Auxiliary Output Data Bit 2                                                                                         |  |

| H17                                                                                              | P3-               | Complementary Primary Output Data Bit 3                                                                             |  |

| H18                                                                                              | P3+               | Primary Output Data Bit 3                                                                                           |  |

|                                                                                                  | ·                 | I .                                                                                                                 |  |

### Pin Description (continued)

| CONTACT | NAME             | FUNCTION                                                                                    |  |

|---------|------------------|---------------------------------------------------------------------------------------------|--|

| J1      | VIN-             | Differential Input Voltage (-)                                                              |  |

| J17     | A3-              | Complementary Auxiliary Output Data Bit 3                                                   |  |

| J18     | A3+              | Auxiliary Output Data Bit 3                                                                 |  |

| K17     | DREADY-          | Complementary Data-Ready Clock                                                              |  |

| K18     | DREADY+          | Data-Ready Clock                                                                            |  |

| L1      | VIN+             | Differential Input Voltage (+)                                                              |  |

| L17     | P4-              | Complementary Primary Output Data Bit 4                                                     |  |

| L18     | P4+              | Primary Output Data Bit 4                                                                   |  |

| M17     | A4-              | Complementary Auxiliary Output Data Bit 4                                                   |  |

| M18     | A4+              | Auxiliary Output Data Bit 4                                                                 |  |

| N17     | P5-              | Complementary Primary Output Data Bit 5                                                     |  |

| N18     | P5+              | Primary Output Data Bit 5                                                                   |  |

| P1      | CLK-             | Complementary Sampling Clock Input                                                          |  |

| P2      | TESTPOINT (T.P.) | This contact <b>must</b> be connected to GNDI.                                              |  |

| P17     | A5-              | Complementary Auxiliary Output Data Bit 5                                                   |  |

| P18     | A5+              | Auxiliary Output Data Bit 5                                                                 |  |

| R1–R3   | CLKCOM           | 50Ω Clock Termination Return                                                                |  |

| R19     | AUXEN1           | Connect to V <sub>CC</sub> O to power the auxiliary port, or connect to GNDD to power down. |  |

| T1      | CLK+             | Sampling Clock Input                                                                        |  |

| U10     | RSTIN-           | Complementary PECL Demux Reset Input                                                        |  |

| U11     | RSTOUT-          | Complementary PECL Reset Output                                                             |  |

| U12     | OR-              | Complementary PECL Overrange Bit                                                            |  |

| U13     | A7-              | Complementary Auxiliary Output Data Bit 7 (MSB)                                             |  |

| U14     | P7-              | Complementary Primary Output Data Bit 7 (MSB)                                               |  |

| U15     | A6-              | Complementary Auxiliary Output Data Bit 6                                                   |  |

| U16     | P6-              | Complementary Primary Output Data Bit 6                                                     |  |

| V10     | RSTIN+           | PECL Demux Reset Input                                                                      |  |

| V11     | RSTOUT+          | PECL Reset Output                                                                           |  |

| V12     | OR+              | PECL Overrange Bit                                                                          |  |

| V13     | A7+              | Auxiliary Output Data Bit 7 (MSB)                                                           |  |

| V14     | P7+              | Primary Output Data Bit 7 (MSB)                                                             |  |

| V15     | A6+              | Auxiliary Output Data Bit 6                                                                 |  |

| V16     | P6+              | Primary Output Data Bit 6                                                                   |  |

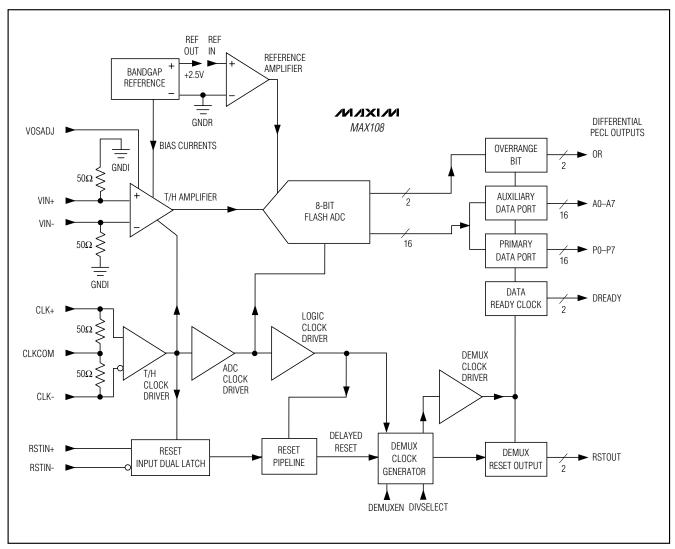

Figure 1. Simplified Functional Diagram

### **Detailed Description**

The MAX108 is an 8-bit, 1.5Gsps flash analog-to-digital converter (ADC) with on-chip T/H amplifier and differential PECL-compatible outputs. The ADC (Figure 1) employs a fully differential 8-bit quantizer and a unique encoding scheme to limit metastable states, with no error exceeding 1LSB max.

An integrated 8:16 output demultiplexer simplifies interfacing to the part by reducing the output data rate to one-half the sampling clock rate. This demultiplexer

has internal reset capability that allows multiple MAX108s to be time-interleaved to achieve higher effective sampling rates.

When clocked at 1.5Gsps, the MAX108 provides a typical ENOB of 7.5 bits at an analog input frequency of 750MHz. The analog input of the MAX108 is designed for differential or single-ended use with a ±250mV full-scale input range. In addition, this fast ADC features an on-chip +2.5V precision bandgap reference. If desired, an external reference can also be used.

#### **Principle of Operation**

The MAX108's flash or parallel architecture provides the fastest multibit conversion of all common integrated ADC designs. The key to this high-speed flash architecture is the use of an innovative, high-performance comparator design. The flash converter and downstream logic translate the comparator outputs into a parallel 8-bit output code and pass this binary code on to the optional 8:16 demultiplexer, where primary and auxiliary ports output PECL-compatible data at up to 750Msps per port (depending on how the demultiplexer section is set on the MAX108).

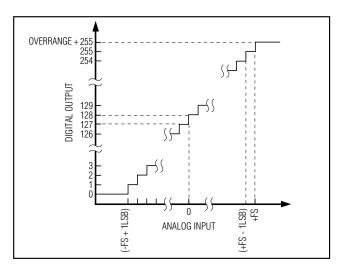

The ideal transfer function appears in Figure 2.

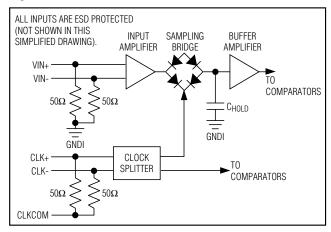

#### **On-Chip Track/Hold Amplifier**

As with all ADCs, if the input waveform is changing rapidly during conversion, ENOB and signal-to-noise ratio (SNR) specifications will degrade. The MAX108's on-chip, wide-bandwidth (2.2GHz) T/H amplifier reduces this effect and increases the ENOB performance significantly, allowing precise capture of fast analog data at high conversion rates.

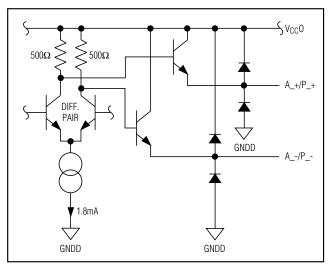

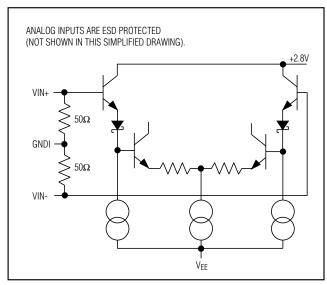

The T/H amplifier buffers the input signal and allows a full-scale signal input range of  $\pm 250$ mV. The T/H amplifier's differential  $50\Omega$  input termination simplifies interfacing to the MAX108 with controlled impedance lines. Figure 3 shows a simplified diagram of the T/H amplifier stage internal to the MAX108.

Aperture width, delay, and jitter (or uncertainty) are parameters that affect the dynamic performance of high-speed converters. Aperture jitter, in particular, directly influences SNR and limits the maximum slew rate (dV/dt) that can be digitized without contributing significant errors. The MAX108's innovative T/H amplifier design limits aperture jitter typically to less than 0.5ps.

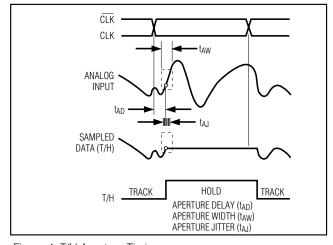

#### Aperture Width

Aperture width (tAW) is the time the T/H circuit requires (Figure 4) to disconnect the hold capacitor from the input circuit (for instance, to turn off the sampling bridge and put the T/H unit in hold mode).

#### Aperture Jitter

Aperture jitter (t<sub>AJ</sub>) is the sample-to-sample variation (Figure 4) in the time between the samples.

#### Aperture Delay

Aperture delay (t<sub>AD</sub>) is the time defined between the rising edge of the sampling clock and the instant when an actual sample is taken (Figure 4).

#### **Internal Reference**

The MAX108 features an on-chip +2.5V precision bandgap reference that can be used by connecting

Figure 2. Transfer Function

Figure 3. Internal Structure of the 2.2GHz T/H Amplifier

Figure 4. T/H Aperture Timing

REFOUT to REFIN. This connects the reference output to the positive input of the reference buffer. The buffer's negative input is internally connected to GNDR. GNDR must be connected to GNDI on the user's application board. If required, REFOUT can source up to 2.5mA to supply external devices.

An adjustable external reference can be used to adjust the ADC's full-scale range. To use an external reference supply, connect a high-precision reference to the REFIN pin and leave the REFOUT pin floating. In this configuration, REFOUT **must not** be simultaneously connected, to avoid conflicts between the two references. REFIN has a typical input resistance of  $5k\Omega$  and accepts input voltages of  $+2.5V \pm 200mV$ . For best performance, Maxim recommends using the MAX108's internal reference.

#### **Digital Outputs**

The MAX108 provides data in offset binary format to differential PECL outputs. A simplified circuit schematic of the PECL output cell is shown in Figure 5. All PECL outputs are powered from VCCO, which may be operated from any voltage between +3.0V to VCCD for flexible interfacing with either +3.3V or +5V systems. The nominal VCCO supply voltage is +3.3V.

All PECL outputs on the MAX108 are open-emitter types and must be terminated at the far end of each transmission line with  $50\Omega$  to  $V_{CC}O$  - 2V. Table 1 lists all MAX108 PECL outputs and their functions.

#### **Demultiplexer Operation**

The MAX108 features an internal demultiplexer that provides for three different modes of operation (see the

Figure 5. Simplified PECL Output Structure

following sections on *Demultiplexed DIV2 Mode, Non-Demultiplexed DIV1 Mode*, and *Decimation DIV4 Mode*) controlled by two TTL/CMOS-compatible inputs: DEMUXEN and DIVSELECT.

DEMUXEN enables or disables operation of the internal 1:2 demultiplexer. A logic high on DEMUXEN activates the internal demultiplexer, and a logic low deactivates it. With the internal demultiplexer enabled, DIVSELECT controls the selection of the operational mode. DIVSELECT low selects demultiplexed DIV2 mode, and DIVSELECT high selects decimation DIV4 mode (Table 2).

**Table 1. PECL Output Functions**

| PECL OUTPUT SIGNALS    | FUNCTIONAL DESCRIPTION                                                                                                                                                                                     |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0+ to P7+, P0- to P7- | Primary-Port Differential Outputs from LSB to MSB. A "+" indicates the true outputs; a "-" denotes the complementary outputs.                                                                              |

| A0+ to A7+, A0- to A7- | Auxiliary-Port Differential Outputs from LSB to MSB. A "+" indicates the true outputs; a "-" denotes the complementary outputs.                                                                            |

| DREADY+, DREADY-       | Data-Ready Clock True and Complementary Outputs. These signal lines are used to latch the output data from the primary to the auxiliary output ports. Data changes on the rising edge of the DREADY clock. |

| OR+, OR-               | Overrange True and Complementary Outputs                                                                                                                                                                   |

| RSTOUT+, RSTOUT-       | Reset Output True and Complementary Outputs                                                                                                                                                                |

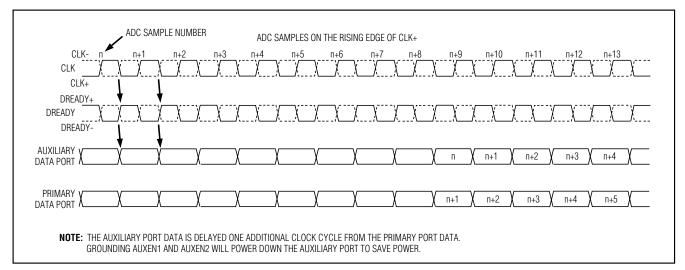

#### Non-Demultiplexed DIV1 Mode

The MAX108 may be operated at up to 750Msps in non-demultiplexed DIV1 mode (Table 2). In this mode, the internal demultiplexer is disabled and sampled data is presented to the primary port only, with the data repeated at the auxiliary port but delayed by one clock cycle (Figure 6). Since the auxiliary output port contains the same data stream as the primary output port, the auxiliary port can be shut down to save power by connecting AUXEN1 and AUXEN2 to digital ground (GNDD). This powers down the internal bias cells and causes both outputs (true and complementary) of the auxiliary port to pull up to a logic-high level. To save additional power, the external  $50\Omega$  termination resistors connected to the PECL termination

power supply (VccO - 2V) may be removed from all auxiliary output ports.

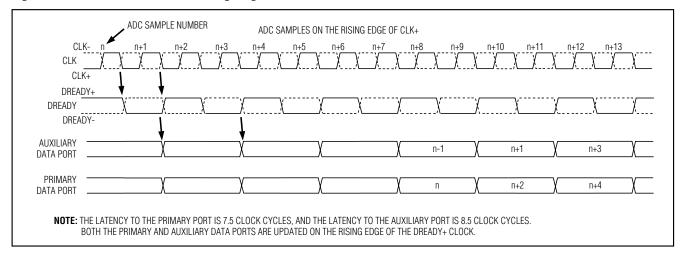

#### Demultiplexed DIV2 Mode

The MAX108 features an internally selectable DIV2 mode (Table 2) that reduces the output data rate to one-half of the sample clock rate. The demultiplexed outputs are presented in dual 8-bit format with two consecutive samples appearing in the primary and auxiliary output ports on the rising edge of the data-ready clock (Figure 7). The auxiliary data port contains the previous sample, and the primary output contains the most recent data sample. AUXEN1 and AUXEN2 must be connected to VCCO to power up the auxiliary port PECL output drives.

Figure 6. Non-Demuxed, DIV1-Mode Timing Diagram

Figure 7. Demuxed DIV2-Mode Timing Diagram

#### **Decimation DIV4 Mode**

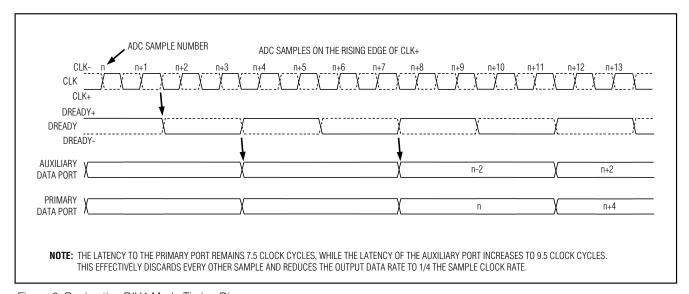

The MAX108 also offers a special decimated, demultiplexed output (Figure 8) that discards every other input sample and outputs data at one-quarter the input sampling rate for system debugging at slower output data rates. With an input clock of 1.5GHz, the effective output data rate will be reduced to 375MHz per output port in the DIV4 mode (Table 2). Since every other sample is discarded, the effective sampling rate is 750Msps.

#### **Overrange Operation**

A single differential PECL overrange output bit (OR+, OR-) is provided for both primary and auxiliary demultiplexed outputs. The operation of the overrange bit depends on the status of the internal demultiplexer. In demultiplexed DIV2 mode and decimation DIV4 mode,

the OR bit will flag an overrange condition if either the primary or auxiliary port contains an overranged sample (Table 2). In non-demultiplexed DIV1 mode, the OR port will flag an overrange condition only when the primary output port contains an overranged sample.

### \_Applications Information

#### **Single-Ended Analog Inputs**

The MAX108 T/H amplifier is designed to work at full speed for both single-ended and differential analog inputs (Figure 9). Inputs VIN+ and VIN- feature on-chip, laser-trimmed  $50\Omega$  termination resistors to provide excellent voltage standing-wave ratio (VSWR) performance.

Figure 8. Decimation DIV4-Mode Timing Diagram

#### **Table 2. Demultiplexer Operation**

| DEMUXEN | DIVSELECT | DEMUX MODE            | OVERRANGE BIT OPERATION                              |

|---------|-----------|-----------------------|------------------------------------------------------|

| Low     | X         | DIV1<br>750Msps (max) | Flags overrange data appearing in primary port only. |

| High    | Low       | DIV2<br>750Msps/port  | Flags overrange data appearing in either             |

| High    | High      | DIV4<br>375Msps/port  | the primary or auxiliary port.                       |

X = Don't care

Figure 9. Simplified Analog Input Structure (Single-Ended/ Differential)

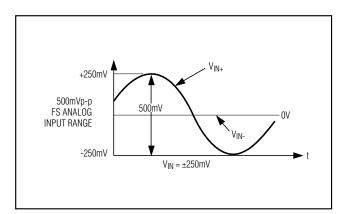

In a typical single-ended configuration, the analog input signal (Figure 10a) enters the T/H amplifier stage at the in-phase input (VIN+), while the inverted phase input (VIN-) is reverse-terminated to GNDI with an external  $50\Omega$  resistor. Single-ended operation allows for an input amplitude of  $\pm 250$ mV. Table 3 shows a selection of input voltages and their corresponding output codes for single-ended operation.

#### **Differential Analog Inputs**

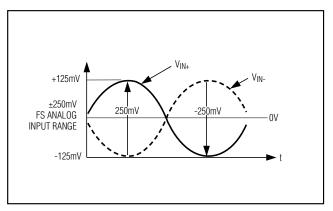

To obtain a full-scale digital output with differential input drive (Figure 10b), 250mVp-p must be applied between VIN+ and VIN- (VIN+ = +125mV, and VIN- = -125mV). Midscale digital output codes (01111111 or 10000000) occur when there is no voltage difference between VIN+ and VIN-. For a zero-scale digital output code, the

Figure 10a. Single-Ended Analog Input Signals

Figure 10b. Differential Analog Input Signals

in-phase (VIN+) input must see -125mV and the inverted input (VIN-) must see +125mV. A differential input drive is recommended for best performance. Table 4 represents a selection of differential input voltages and their corresponding output codes.

Table 3. Ideal Input Voltage and Output Code Results for Single-Ended Operation

| VIN+          | VIN- | OVERRANGE BIT | OUTPUT CODE                     |

|---------------|------|---------------|---------------------------------|

| +250mV        | OV   | 1             | 1111111 (full scale)            |

| +250mV - 1LSB | OV   | 0             | 11111111                        |

| OV            | OV   | 0             | 01111111<br>toggles<br>10000000 |

| -250mV + 1LSB | OV   | 0             | 0000001                         |

| -250mV        | OV   | 0             | 00000000 (zero scale)           |

#### Table 4. Ideal Input Voltage and Output Code Results for Differential Operation

| VIN+            | VIN-            | OVERRANGE BIT | OUTPUT CODE                     |  |  |  |

|-----------------|-----------------|---------------|---------------------------------|--|--|--|

| +125mV          | -125mV          | 1             | 11111111 (full scale)           |  |  |  |

| +125mV - 0.5LSB | -125mV + 0.5LSB | 0             | 11111111                        |  |  |  |

| OV              | OV              | 0             | 01111111<br>toggles<br>10000000 |  |  |  |

| -125mV + 0.5LSB | +125mV - 0.5LSB | 0             | 0000001                         |  |  |  |

| -125mV          | -125mV +125mV   |               | 00000000 (zero scale)           |  |  |  |

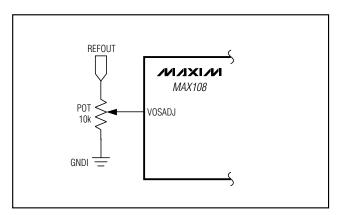

#### Offset Adjust

The MAX108 provides a control input (VOSADJ) to compensate for system offsets. The offset adjust input is a self-biased voltage divider from the internal +2.5V precision reference. The nominal open-circuit voltage is one-half the reference voltage. With an input resistance of typically  $25k\Omega$ , this pin may be driven by an external  $10k\Omega$  potentiometer (Figure 11) connected between REFOUT and GNDI to correct for offset errors. This control provides a typical  $\pm 5.5 LSB$  offset adjustment range.

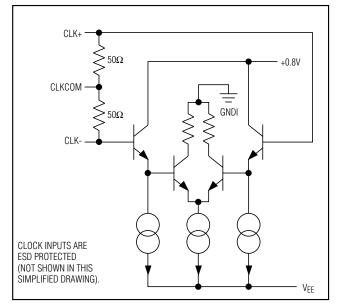

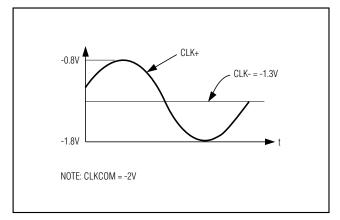

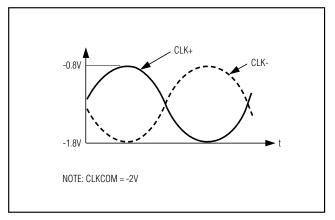

#### **Clock Operation**

The MAX108 clock inputs are designed for either single-ended or differential operation (Figure 12) with flexible input drive requirements. Each clock input is terminated with an on-chip, laser-trimmed  $50\Omega$  resistor to CLKCOM (clock-termination return). The CLKCOM termination voltage can be connected anywhere between ground and -2V for compatibility with standard ECL drive levels.

The clock inputs are internally buffered with a preamplifier to ensure proper operation of the data converter, even with small-amplitude sine-wave sources. The MAX108 was designed for single-ended, low-phase-noise sine-wave clock signals with as little as 100mV amplitude (-10dBm). This eliminates the need for an external ECL clock buffer and its added jitter.

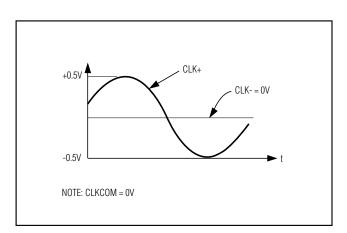

#### Single-Ended Clock Inputs (Sine-Wave Drive)

Excellent performance is obtained by AC- or DC-coupling a low-phase-noise sine-wave source into a single clock input (Figure 13a, Table 5). For proper DC balance, the undriven clock input should be externally  $50\Omega$  reverse-terminated to GNDI.

The dynamic performance of the data converter is essentially unaffected by clock-drive power levels from -10dBm (100mV clock signal amplitude) to +10dBm (1V clock signal amplitude). The MAX108 dynamic per-

Figure 11. Offset Adjust with External  $10k\Omega$  Potentiometer

Figure 12. Simplified Clock Input Structure (Single-Ended/ Differential)

formance specifications are determined by a singleended clock drive of +4dBm (500mV clock signal amplitude). To avoid saturation of the input amplifier stage, limit the clock power level to a maximum of +10dBm.

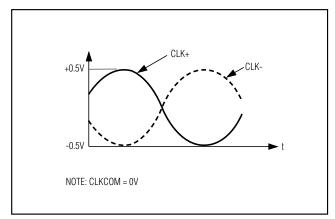

#### Differential Clock Inputs (Sine-Wave Drive)

The advantages of differential clock drive (Figure 13b, Table 5) can be obtained by using an appropriate balun or transformer to convert single-ended sine-wave sources into differential drives. The precision on-chip, laser-trimmed  $50\Omega$  clock-termination resistors ensure excellent amplitude matching. See *Single-Ended Clock Inputs (Sine-Wave Drive)* for proper input amplitude requirements.

#### Single-Ended Clock Inputs (ECL Drive)

Configure the MAX108 for single-ended ECL clock drive by connecting the clock inputs as shown in Figure 13c (Table 5). A well-bypassed VBB supply (-1.3V) is essential to avoid coupling noise into the undriven clock input, which would degrade dynamic performance.

#### Differential Clock Inputs (ECL Drive)

Drive the MAX108 from a standard differential (Figure 13d, Table 5) ECL clock source by setting the clock termination voltage at CLKCOM to -2V. Bypass the clock-termination return (CLKCOM) as close to the ADC as possible with a 0.01µF capacitor connected to GNDI.

Figure 13a. Single-Ended Clock Input Signals

Figure 13b. Differential Clock Input Signals

Figure 13c. Single-Ended ECL Clock Drive

Figure 13d. Differential ECL Clock Drive

### Table 5. DC-Coupled Clock Drive Options

| CLOCK DRIVE            | CLK+            | CLK-                 | CLKCOM | REFERENCE  |

|------------------------|-----------------|----------------------|--------|------------|

| Single-Ended Sine Wave | -10dBm to +4dBm | External 50Ω to GNDI | GNDI   | Figure 13a |

| Differential Sine Wave | -10dBm to +4dBm | -10dBm to +4dBm      | GNDI   | Figure 13b |

| Single-Ended ECL       | ECL Drive       | -1.3V                | -2V    | Figure 13c |

| Differential ECL       | ECL Drive       | ECL Drive            | -2V    | Figure 13d |

#### **AC-Coupling Clock Inputs**

The clock inputs CLK+ and CLK- can be driven with PECL logic if the clock inputs are AC-coupled. Under this condition, connect CLKCOM to GNDI. Single-ended ECL/PECL/sine-wave drive is also possible if the undriven clock input is reverse-terminated to GNDI through a  $50\Omega$  resistor in series with a capacitor whose value is identical to that used to couple the driven input.

#### **Demux Reset Operation**

The MAX108 features an internal 1:2 demultiplexer that reduces the data rate of the output digital data to one-half the sample clock rate. Demux reset is necessary when interleaving multiple MAX108s and/or synchronizing external demultiplexers. The simplified block diagram of Figure 1 shows that the demux reset signal path consists of four main circuit blocks. From input to output, they are the reset input dual latch, the reset pipeline, the demux clock generator, and the reset output. The signals associated with the demux reset operation and the control of this section are listed in Table 6.

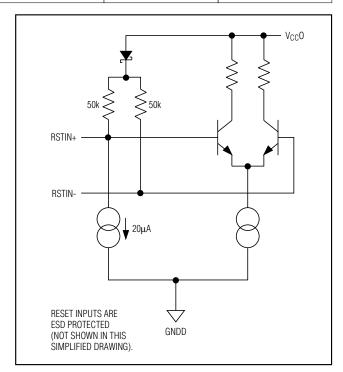

#### Reset Input Dual Latch

The reset input dual-latch circuit block accepts differential PECL reset inputs referenced to the same  $V_{CCO}$  power supply that powers the MAX108 PECL outputs. For applications that do not require a synchronizing reset, the reset inputs can be left open. In this case, they will self-bias to a proper level with internal  $50k\Omega$  resistors and  $20\mu A$  current source. This combination creates a -1V difference between RSTIN+ and RSTIN-to disable the internal reset circuitry. When driven with PECL logic levels terminated with  $50\Omega$  to (VCCO - 2V), the internal biasing network can easily be overdriven. Figure 14 shows a simplified schematic of the reset input structure.

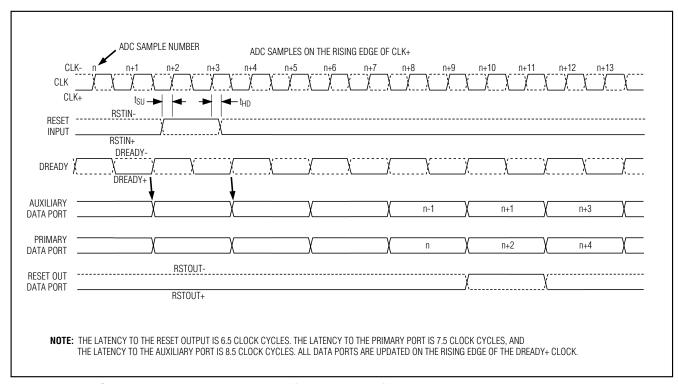

To properly latch the reset input data, the setup time ( $t_{SU}$ ) and the data-hold time ( $t_{HD}$ ) must be met with respect to the rising edge of the sample clock. The timing diagram of Figure 15 shows the timing relationship of the reset input and sampling clock.

Figure 14. Simplified Reset Input Structure

Figure 15. Reset Input Timing Definitions

**Table 6. Demux Operating and Reset Control Signals**

| SIGNAL NAME                                | TYPE                      | FUNCTION                                                                   |

|--------------------------------------------|---------------------------|----------------------------------------------------------------------------|

| CLK+, CLK-                                 | Sampling clock inputs     | Master ADC timing signal. The ADC samples on the rising edge of CLK+.      |

| DREADY+, DREADY- Differential PECL outputs |                           | Data-Ready PECL Output. Output data changes on the rising edge of DREADY+. |

| RSTIN+, RSTIN-                             | Differential PECL inputs  | Demux reset input signals. Resets the internal demux when asserted.        |

| RSTOUT+, RSTOUT-                           | Differential PECL outputs | Reset outputs for resetting additional external demux devices.             |

#### Reset Pipeline

The next section in the reset signal path is the reset pipeline. This block adds clock cycles of latency to the reset signal to match the latency of the converted analog data through the ADC. In this way, when reset data arrives at the RSTOUT+/RSTOUT- PECL output it will be time-aligned with the analog data present in the primary and auxiliary ports at the time the reset input was deasserted at RSTIN+/RSTIN-.

#### **Demux Clock Generator**

The demux clock generator creates the DIV1, DIV2, or DIV4 clocks required for the different modes of demux and non-demultiplexed operation. The TTL/CMOS control inputs DEMUXEN and DIVSELECT control the demuxed mode selection, as described in Table 2. The timing diagrams in Figures 16 and 17 show the output timing and data alignment in DIV1, DIV2, and DIV4 modes, respectively.

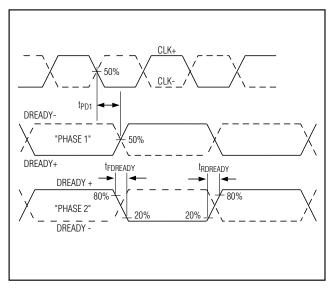

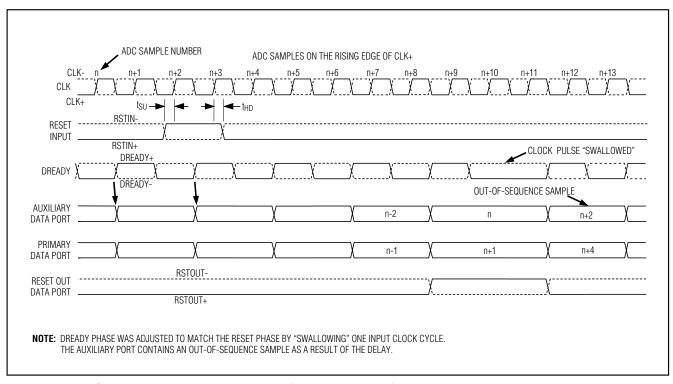

The phase relationship between the sampling clock at the CLK+/CLK- inputs and the data-ready clock at the Dready+/Dready- outputs will be random at device power-up. As with all divide-by-two circuits, two possible phase relationships exist between these clocks. The difference between the phases is simply the inversion of the DIV2-Dready clock. The timing diagram in Figure 16 shows this relationship.

Reset all MAX108 devices to a known DREADY phase after initial power-up for applications such as interleaving, where two or more MAX108 devices are used to achieve higher effective sampling rates. This synchronization is necessary to set the order of output samples between the devices. Resetting the converters accomplishes this synchronization. The reset signal is used to force the internal counter in the demux clock-generator block to a known phase state.

Figure 16. CLK and DREADY Timing in Demuxed DIV2 Mode Showing Two Possible DREADY Phases

Figure 17. Output Timing for All Modes (DIV1, DIV2, DIV4)

#### Reset Output

Finally, the reset signal is presented in differential PECL format to the last block of the reset signal path. RSTOUT+/RSTOUT- output the time-aligned reset signal, used for resetting additional external demuxes in applications that need further output data-rate reduction. Many demux devices require their reset signal to be asserted for several clock cycles while they are clocked. To accomplish this, the MAX108 DREADY clock will continue to toggle while RSTOUT is asserted.

When a single MAX108 device is used, no synchronizing reset is required because the order of the samples in the output ports is unchanged, regardless of the phase of the DREADY clock. In DIV2 mode, the data in the auxiliary port is delayed by 8.5 clock cycles, while the data in the primary port is delayed by 7.5 clock cycles. The older data is always in the auxiliary port, regardless of the phase of the DREADY clock.

The reset output signal, RSTOUT, is delayed by one fewer clock cycles (6.5 clock cycles) than the primary

port. The reduced latency of RSTOUT serves to mark the start of synchronized data in the primary and auxiliary ports. When the RSTOUT signal returns to a zero, the DREADY clock phase is reset.

Since there are two possible phases of the DREADY clock with respect to the input clock, there are two possible timing diagrams to consider. The first timing diagram (Figure 18) shows the RSTOUT timing and data alignment of the auxiliary and primary output ports when the DREADY clock phase is already reset. For this example, the RSTIN pulse is two clock cycles long. Under this condition, the DREADY clock continues uninterrupted, as does the data stream in the auxiliary and primary ports.

The second timing diagram (Figure 19) shows the results when the DREADY phase is opposite from the reset phase. In this case, the DREADY clock "swallows" a clock cycle of the sample clock, resynchronizing to the reset phase. Note that the data stream in the auxiliary and primary ports has reversed. Before reset was

Figure 18. Reset Output Timing in Demuxed DIV2 Mode (DREADY Aligned)

Figure 19. Reset Output Timing in Demuxed DIV2 Mode (DREADY Realigned)

asserted, the auxiliary port contained "even" samples while the primary port contained "odd" samples. After the RSTOUT is deasserted (which marks the start of the DREADY clock's reset phase), note that the order of the samples in the ports has been reversed. The auxiliary port also contains an out-of-sequence sample. This is a consequence of the "swallowed" clock cycle that was needed to resynchronize DREADY to the reset phase. Also note that the older sample data is always in the auxiliary port, regardless of the DREADY phase.

These examples illustrate the combinations that result with a reset input signal of two clock cycles. It is also possible to reset the internal MAX108 demux successfully with a reset pulse of only one clock cycle, provided that the setup time and hold-time requirements are met with respect to the sample clock. However, this is not recommended when additional external demuxes are used.

Note that many external demuxes require their reset signals to be asserted while they are clocked, and may require more than one clock cycle of reset. More importantly, if the phase of the DREADY clock is such that a clock pulse will be "swallowed" to resynchronize, then

no reset output will occur at all. In effect, the RSTOUT signal will be "swallowed" with the clock pulse. The best method to ensure complete system reset is to assert RSTIN for the appropriate number of DREADY clock cycles required to complete reset of the external demuxes.

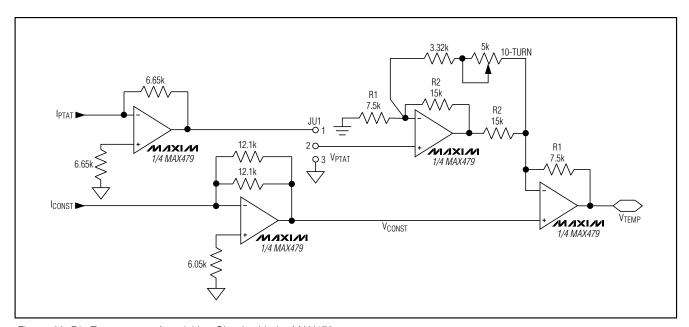

#### **Die Temperature Measurement**

For applications that require monitoring of the die temperature, it is possible to determine the die temperature of the MAX108 under normal operating conditions by observing the currents ICONST and IPTAT, at contacts ICONST and IPTAT. ICONST and IPTAT are two 100µA (nominal) currents that are designed to be equal at +27°C. These currents are derived from the MAX108's internal precision +2.5V bandgap reference. ICONST is designed to be temperature independent, while IPTAT is directly proportional to the absolute temperature. These currents are derived from PNP current sources referenced from VCCI and driven into two series diodes connected to GNDI. The contacts ICONST and IPTAT may be left open because internal catch diodes prevent saturation of the current sources. The simplest method of determining the die temperature is to measure each

current with an ammeter (which shuts off the internal catch diodes) referenced to GNDI. The die temperature in °C is then calculated by the expression:

$$T_{DIE} = 300 \left[ \frac{I_{PTAT}}{I_{CONST}} \right] - 273$$

Another method of determining the die temperature uses the operational amplifier circuit shown in Figure 20. The circuit produces a voltage that is proportional to the die temperature. A possible application for this signal is speed control for a cooling fan to maintain constant MAX108 die temperature. The circuit operates by converting the ICONST and IPTAT currents to voltages VCONST and VPTAT, with appropriate scaling to account for their equal values at +27°C. This voltage difference is then amplified by two amplifiers in an instrumentation-amplifier configuration with adjustable gain. The nominal value of the circuit gain is 4.5092V/V. The gain of the instrumentation amplifier is given by the expression:

$$A_{V} = \frac{V_{TEMP}}{V_{CONST} - V_{PTAT}}$$

$$A_V = 1 + \frac{R1}{R2} + 2\frac{R1}{R3}$$

To calibrate the circuit, first connect pins 2 and 3 on JU1 to zero the input of the PTAT path. With the MAX108 powered up, adjust potentiometer R3 until the voltage at the VTEMP output is -2.728V. Connecting pins 1 and 2 on JU1 restores normal operation to the circuit after the calibration is complete. The voltage at the VTEMP node will then be proportional to the actual MAX108 die temperature according to the equation:

TDIE (

$$^{\circ}$$

C) = 100 VTEMP

The overall accuracy of the die temperature measurement using the operational-amplifier scaling circuitry is limited mainly by the accuracy and matching of the resistors in the circuit.

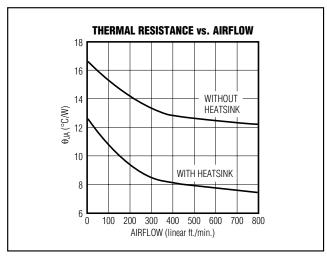

#### Thermal Management

Depending on the application environment for the ESBGA-packaged MAX108, the customer may have to apply an external heatsink to the package after board assembly. Existing open-tooled heatsinks are available from standard heatsink suppliers (see *Heatsink Manufacturers*). The heatsinks are available with preapplied adhesive for easy package mounting.

Figure 20. Die Temperature Acquisition Circuit with the MAX479

Table 7. Thermal Performance for MAX108 With or Without Heatsink

| AIDELOW                    | MAX108 θJA (°C/W)   |               |  |  |  |  |  |  |  |

|----------------------------|---------------------|---------------|--|--|--|--|--|--|--|

| AIRFLOW<br>(linear ft/min) | WITHOUT<br>HEATSINK | WITH HEATSINK |  |  |  |  |  |  |  |

| 0                          | 16.5                | 12.5          |  |  |  |  |  |  |  |

| 200                        | 14.3                | 9.4           |  |  |  |  |  |  |  |

| 400                        | 13                  | 8.3           |  |  |  |  |  |  |  |

| 800                        | 12.5                | 7.4           |  |  |  |  |  |  |  |

#### Thermal Performance

The MAX108 has been modeled to determine the thermal resistance from junction to ambient. Table 7 lists the ADC's thermal performance parameters:

Ambient Temperature:  $T_A = +70^{\circ}C$

Heatsink Dimensions: 25mm x 25mm x 10mm

PC Board Size and Layout: 4 in. x 4 in.

2 Signal Layers2 Power Layers

#### Heatsink Manufacturers

Aavid Engineering and IERC provide open-tooled, low-profile heatsinks, fitting the 25mm x 25mm ESBGA package.

Aavid Engineering, Inc. Phone: 714-556-2665

Heatsink Catalog No.: 335224B00032

Heatsink Dimensions: 25mm x 25mm x 10mm

International Electronic Research Corporation (IERC)

Phone: 818-842-7277

Heatsink Catalog No.: BDN09-3CB/A01

Heatsink Dimensions: 23.1mm x 23.1mm x 9mm

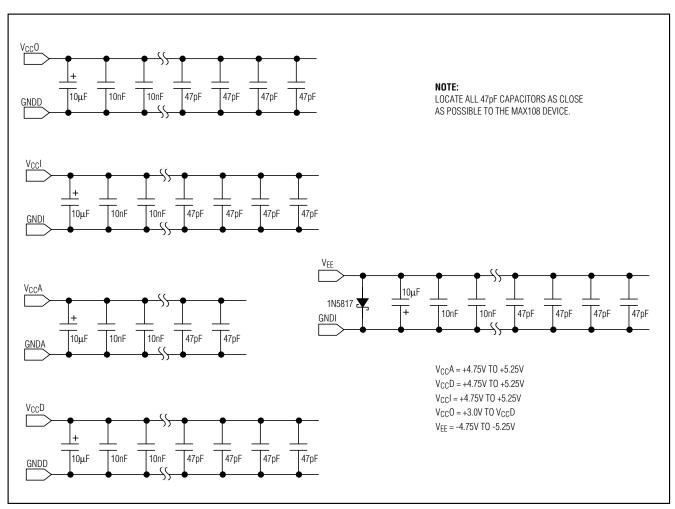

#### **Bypassing/Layout/Power Supply**

Grounding and power-supply decoupling strongly influence the MAX108's performance. At a 1.5GHz clock frequency and 8-bit resolution, unwanted digital crosstalk may couple through the input, reference, power-supply, and ground connections and adversely influence the dynamic performance of the ADC. Therefore, closely follow the grounding and power-supply decoupling guidelines (Figure 22).

Figure 21. MAX108 Thermal Performance

Maxim strongly recommends using a multilayer printed circuit board (PCB) with separate ground and power-supply planes. Since the MAX108 has separate analog and digital ground connections (GNDA, GNDI, GNDR, and GNDD, respectively), the PCB should feature separate analog and digital ground sections connected at only one point (star ground at the power supply). Digital signals should run above the digital ground plane, and analog signals should run above the analog ground plane. Keep digital signals far away from the sensitive analog inputs, reference inputs, and clock inputs. Highspeed signals, including clocks, analog inputs, and digital outputs, should be routed on  $50\Omega$  microstrip lines, such as those employed on the MAX108 evaluation kit.

The MAX108 has separate analog and digital power-supply inputs: VEE (-5V analog and substrate supply) and VCCI (+5V) to power the T/H amplifier, clock distribution, bandgap reference, and reference amplifier; VCCA (+5V) to supply the ADC's comparator array; VCCO (+3V to VCCD) to establish power for all PECL-based circuit sections; and VCCD (+5V) to supply all logic circuits of the data converter.

The MAX108 VEE supply contacts **must not** be left open while the part is being powered up. To avoid this condition, add a high-speed Schottky diode (such as a Motorola 1N5817) between VEE and GNDI. This diode prevents the device substrate from forward biasing, which could cause latchup.

All supplies should be decoupled with large tantalum or electrolytic capacitors at the point they enter the PCB. For best performance, bypass all power supplies to the appropriate ground with a  $10\mu F$  tantalum capacitor to filter power-supply noise, in parallel with a  $0.1\mu F$  capacitor and a high-quality 47pF ceramic chip capacitor located very close to the MAX108 device to filter very high-frequency noise.

#### **Static Parameter Definitions**

#### Integral Nonlinearity

Integral nonlinearity (INL) is the deviation of the values on an actual transfer function from a straight line. This straight line can be either a best-straight-line fit or a line drawn between the endpoints of the transfer function, once offset and gain errors have been nullified. The static linearity parameters for the MAX108 are measured using the best-straight-line fit method.

#### **Differential Nonlinearity**

Differential nonlinearity (DNL) is the difference between an actual step width and the ideal value of 1LSB. A DNL error specification of less than 1LSB guarantees no missing codes and a monotonic transfer function.

Figure 22. MAX108 Bypassing and Grounding

#### Bit Error Rates

Errors resulting from metastable states may occur when the analog input voltage (at the time the sample is taken) falls close to the decision point of any one of the input comparators. Here, the magnitude of the error depends on the location of the comparator in the comparator network. If it is the comparator for the MSB, the error will reach full scale. The MAX108's unique encoding scheme solves this problem by limiting the magnitude of these errors to 1LSB.

### **Dynamic Parameter Definitions**

#### Signal-to-Noise Ratio

For a waveform perfectly reconstructed from digital samples, the theoretical maximum SNR is the ratio of the full-scale analog input (RMS value) to the RMS quantization error (residual error). The ideal, theoretical minimum analog-to-digital noise is caused by quantization error only and results directly from the ADC's resolution (N bits):

$$SNR(MAX) = (6.02 N + 1.76)dB$$

In reality, there are other noise sources besides quantization noise: thermal noise, reference noise, clock jitter, etc. SNR is calculated by taking the ratio of the RMS signal to the RMS noise, which includes all spectral components minus the fundamental, the first five harmonics, and the DC offset.

#### Effective Number of Bits

ENOB indicates the global accuracy of an ADC at a specific input frequency and sampling rate. An ideal ADC's error consists of quantization noise only. ENOB is calculated from a curve fit referenced to the theoretical full-scale range.

#### Signal-to-Noise Plus Distortion

Signal-to-Noise plus distortion (SINAD) is calculated from the ENOB as follows:

$$SINAD = (6.02 ENOB) + 1.76$$

#### **Total Harmonic Distortion**

Total harmonic distortion (THD) is the ratio of the RMS sum of the first five harmonics of the input signal to the fundamental itself. This is expressed as:

THD = 20 log

$$\left(\sqrt{\left({V_2}^2 + {V_3}^2 + {V_4}^2 + {V_5}^2\right)} / V_1\right)$$

where  $V_1$  is the fundamental amplitude, and  $V_2$  through  $V_5$  are the amplitudes of the 2nd- through 5th-order harmonics.

#### Spurious-Free Dynamic Range

Spurious-free dynamic range (SFDR) is the ratio, expressed in decibels, of the RMS amplitude of the fundamental (maximum signal component) to the RMS value of the next largest spurious component, excluding DC offset.

#### Intermodulation Distortion

The two-tone intermodulation distortion (IMD) is the ratio, expressed in decibels, of either input tone to the worst 3rd-order (or higher) intermodulation products. The input tone levels are at -7dB full scale.

### Chip Information

TRANSISTOR COUNT: 20,486 SUBSTRATE CONNECTED TO VEE

### **Typical Operating Circuit**

### 192-Contact ESBGA PCB Land Pattern